生成AIの急速な進化により、データセンター設計は演算性能中心からI/O効率重視へと大きく転換しつつあります。GPU間通信の増大に伴い、電気I/Oの効率や電力消費が重要な設計課題となる中、光電融合による新しいインターコネクト技術として、米国NVIDIA社が推進するCPO(Co-Packaged Optics)が注目されています。CPOは、GPU・スイッチ・ネットワークを含むAIインフラ全体の通信効率と電力効率を高めるための重要な実装アーキテクチャとして位置付けられています。

本記事では、NVIDIAのCPOがもたらすアーキテクチャ変革と物理層要件を整理するとともに、CPO向けレーザー開発・評価を支援するSYCATUSの計測ソリューションやELSFP光源の取り組みについても紹介します。

目次

- 1. AI時代のデータセンター経済とI/Oの壁

- 2. 光電融合が描く次世代インフラのロードマップ

- 3. CPOアーキテクチャがもたらす構造転換

- 4. CPOが要求する物理層(PHY)要件

- 5. SYCATUSが支援するCPOレーザー開発の最前線

- 6. 2025年以降もNVIDIA CPOが注目される理由

- 7. CPOレーザー評価関連製品に関するお問い合わせ

1. AI時代のデータセンター経済とI/Oの壁

AIモデル巨大化によるGPU間通信 ― NVIDIA NVLinkの進化

生成AIや大規模言語モデル(LLM)の進化により、データセンターにおける性能競争の主戦場は、単純な演算性能からGPU間通信(I/O)へと移行しつつあります。

NVIDIAはNVLinkを中心とした高速インターコネクトによってGPUスケーリングを実現してきました。Blackwell世代では第5世代NVLinkおよびNVLink Switchが導入され、単一GPUあたり最大1.8TB/sの帯域を実現し、最大576 GPUを接続可能なインフラが整備されています。

その一方で、AIクラスタのさらなる大規模化に伴い、システム全体として求められる通信帯域および電力効率への要求は引き続き増大しており、I/Oアーキテクチャの進化が重要なテーマとなっています。

データセンター運営コスト(電力・ラック密度)への圧力

AIモデルの巨大化により、以下のような課題が顕在化しています。

- GPU間通信量の指数関数的増加

- スイッチASICのポート数・帯域の限界

- 電気I/Oに起因する伝送損失と消費電力の増大

電気I/Oの限界が GPU/switch(スイッチ)性能の向上の足枷になっている現状

上記の結果、データセンター運営側には、電力コスト・ラック密度・冷却能力という三重の制約が強くのしかかっています。電気I/Oがシステム全体のボトルネックとなり、もはやGPUやスイッチ単体の性能を向上させるだけでは、AI処理能力の向上は見込めません。

NVIDIAがCPO(Co-Packaged Optics)にコミットすることで市場に与えるインパクト

このような背景の中で、NVIDIAがCPO(Co-Packaged Optics)に本格的にコミットしている点は、単なる技術トレンドの採用ではありません。それは、「AIファブリックの主導権を握る戦略的選択」と捉えるべき動きです。

I/Oを制する企業が、次世代AIインフラのアーキテクチャを定義する。CPOは、その中核を担う技術となります。

“AIファブリックの主導権”を握ることの産業的価値

AIファブリックの主導権を握ることは、AIの計算基盤を支配することで産業競争力を大きく高める重要な要素です。データセンターの効率化、コストおよび環境負荷の削減、AI性能の最大化を実現し、業界標準を主導することで競争優位を確立できます。

さらに、フォトニクスや量子コンピューティングといった先端技術との連携により、新たな市場やビジネスモデルを創出し、将来の産業構造を左右する基盤となります。

2. 光電融合が描く次世代インフラのロードマップ

電気配線では到達不可能なエネルギー効率(pJ/bit)の壁

電気I/Oは配線長が伸びるほど、

- 損失補償のためのSerDes消費電力の増大

- クロックジッタやSI(Signal Integrity)の劣化

を避けることができません。また電気配線はインピーダンス(*)が低いため消費電力がさらに増大します。

現在の最先端技術において、特定条件下では1 pJ/bit未満を達成する事例も報告されています。しかし、データセンター規模での実装や高帯域SerDes、長距離配線を含む実システム環境では、数pJ/bit級のエネルギー効率が一つの設計指標となっているのが実情です。

一方で光インターコネクトは、

- 距離に依存しない低損失特性

- 広帯域・低消費電力

という利点を持ち、pJ/bit以下の世界を現実的な選択肢とします。

*インピーダンス:交流回路における電気抵抗(電流の流れにくさ)を示す指標。通信に必要とされる電圧振幅に対し、インピーダンスが低いほど消費電力は大きい。

CPOがNVIDIA Quantum-XのGPU(Blackwell/Rubin)・switch(スイッチ)の中心技術になる理由

NVIDIA Quantum-Xは、

- GPU(Blackwell / Rubin)

- NVLink switch(スイッチ)

- データセンターネットワーク

を一体として最適化するAIファブリックアーキテクチャです。

この構造において、「電気から光への変換をどこで行うか」は、システム全体の効率を決定づける重要な要素となります。

CPOは、

- 光エンジンをスイッチ/SoCパッケージに直接統合

- 電気配線長をmmオーダーまで短縮

することで、I/Oエネルギーとスケーラビリティの問題を同時に解決します。

補足①:NVIDIA Quantum / Quantum-Xとは

NVIDIA QuantumはInfiniBandをベースとした高速ネットワークプラットフォームであり、Quantum-XはAIデータセンター全体を一つの計算基盤として最適化する設計思想を指します。

シリコンフォトニクスを統合したNVIDIAのCo-Packaged Optics(CPO)スイッチは、次世代AI向けネットワーキング基盤として位置付けられています。NVIDIAは、従来のプラガブル構成と比較して大幅な電力効率向上およびネットワーク回復性向上を実現すると説明しています。(参照:NVIDIA シリコンフォトニクス│NVIDIA Corporation)

補足②:NVIDIA CPOに参画する企業例 ― TSMCなど

NVIDIAは、CPOの設計や実装において各パートナー企業が具体的にどの領域を担当しているかについては詳細を公開していません。しかし、これまでに公表されている情報から、CPOエコシステムには、Ayar Lab, Browave、Coherent、Corning、Fabrinet、Foxconn、Lumentum、Senko、SPIL、住友電気工業、TFC、そしてTSMCなど、光デバイス、パッケージング、製造技術に強みを持つ企業が参画していることが分かっています。

これらの企業群は、光エンジン、光ファイバ接続、先端パッケージ、量産プロセスといった多様な技術領域を支え、NVIDIA CPOを実現する産業基盤を形成しています。

参考資料:Nvidia's CPO is the First Step in a Long Journey│LightCounting

Coherent CPO/SiPh(silicon+photonics)/Chiplet統合などの将来展望

Coherent CPO、シリコンフォトニクス(SiPh)、Chiplet統合は、将来のデータセンターやAI基盤を支える中核技術として期待されています。これらを統合することで、高速・低消費電力・高集積な通信と計算が可能となり、データセンターの効率化や持続可能性が大きく向上します。

従来のOSFP方式はどこで課題が生じるか

一方で、従来のOSFPなどのプラガブル光モジュール方式では、スイッチやサーバーフロントパネルにモジュールを配置する構成が一般的であり、ASICやGPUからモジュールまでの電気配線距離が比較的長くなる場合があります。この電気配線区間では信号損失や消費電力が増加するため、伝送品質を維持するためのイコライザなどの補償回路が必要になります。

OSFPモジュール自体は高密度実装や高出力動作に適した優れた熱設計を備えていますが、AIクラスタのさらなる帯域拡張や電力効率向上を目指す中で、電気配線長をさらに短縮する新しいアーキテクチャとしてCPOが検討されています。

3. CPOアーキテクチャがもたらす構造転換

CPOの本質は、光モジュールの小型化だけではありません。システム設計思想そのものの転換にあります。

光エンジンをパッケージに統合する概念的メリット

CPOでは、光I/OがSoCの直近に配置されます。これにより、SerDesから光変換までの距離がmm級となり、損失・反射・ノイズの放出・混入が大幅に削減されます。

SerDes距離がmm級になることの意味(損失・SI改善)

SerDes配線長の短縮により、

- TX/RX補償回路の簡素化

- 消費電力の削減

- SI(Signal Integrity)マージンの拡大

が可能となります。これは、従来のボードレベル設計では到達できなかった領域です。

「電気 → 光」の変換ポイントが移動することで生じる設計哲学の変化

電気から光への変換ポイントがプロセッサ近傍へ移動することで、I/O設計は「分業、境界規格、マージン積み上げ設計」から、「統合、ボーダレス、性能最大化設計」へと転換します。

PCB伝送路不要化・コネクタ不要化がもたらす信号損失/パワーの削減

PCB伝送路やコネクタ削減により、信号損失や消費電力が低減され、よりシンプルで高効率なシステム設計が可能になります。これにより、性能向上と運用コスト削減の両立が実現します。

アライメント・実装・信頼性・保守性などのCPO特有の課題

一方でCPOには、サブミクロン級の高精度アライメント、実装歩留まり、長期信頼性、保守性といった特有の課題があります。特に、レーザー特性や熱管理、故障時の交換困難性への対応が重要です。これらの課題を標準化や設計工夫で克服することが、CPOを中心とした次世代インフラの本格普及と競争力確保の鍵となります。

4. CPOが要求する物理層(PHY)要件

CPOでは、光・電気・熱・機構を個別に最適化する従来の設計手法が通用しません。パッケージ内部で光電融合が行われることにより、物理層(PHY)要件はこれまで以上に厳しく、かつ相互依存性の高いものとなります。

以下では、CPOにおいて特に重要となるPHY要件を整理します。

SiPhモジュレーター(シリコンフォトニクスモジュレーター)

CPOにおける光変調器は、シリコンフォトニクス(SiPh)を前提とした高速・低損失設計が求められます。パッケージ内実装という制約の中で、帯域、消費電力、熱安定性を同時に満たす必要があり、電気ドライバや制御回路との協調設計が重要になります。

PAM4 → 将来のコヒーレントCPOの展開

現行世代ではPAM4変調が主流ですが、さらなる帯域拡張やリンク距離の柔軟性を考慮すると、将来的にはコヒーレントCPOへの展開も視野に入ります。その場合、レーザー線幅や位相雑音への要求は一段と厳しくなり、PHY設計の前提条件そのものが変化します。

レーザーのノイズ特性(RIN・線幅)

レーザーのRIN(Relative Intensity Noise: 相対強度雑音)および線幅は、CPOシステム全体のSNRやマージンを左右する重要なパラメータです。特に、光源共用・高密度実装環境では、レーザーのわずかなノイズ特性の差が多数のリンクの性能に影響するため、定量的な評価と管理が不可欠です。

CPO向けレーザーの評価においては、RINや線幅を含む光ノイズ特性を高帯域かつ高分解能で測定し、実際のPHY要件に即して評価することが求められます。これらの測定・解析を可能にするSYCATUSのレーザー評価製品一覧はこちらをご覧ください。

光ファイバアレイ結合・レンズアレイ・サブミクロンアライメント

CPOでは、光ファイバアレイやレンズアレイを用いた高密度光結合が前提となります。このため、サブミクロン精度のアライメント技術が必須となり、機械的公差、温度変動、長期信頼性を含めた総合的な実装技術が求められます。

超短距離SerDes(224G/112G)のインピーダンス・ジッタ・CTLE/DFE要件

電気側では、112Gおよび224Gクラスの超短距離SerDesが用いられます。配線長がmm級となることでチャネル特性は大きく変化し、インピーダンス不整合、ジッタ、CTLEやDFEの設計思想も従来とは異なる最適解が必要になります。

チャネル損失上限(<5 dB級)の時代へ

CPOでは、ASICと光エンジンが同一パッケージ内に配置されるため、電気チャネル長が大幅に短縮されます。その結果、従来のボードレベル伝送と比較してチャネル損失を大きく低減できる可能性があります。

このような低損失環境では、SerDes設計やPHYマージン設計の最適化のアプローチが変化する可能性があります。ただし、高速信号伝送においてイコライザなどの補償回路は依然として重要な役割を担っており、CPO環境においても適切な設計と最適化が求められます。

クロック同期・タイミングバジェット再設計

CPOでは、従来のボードレベル設計とは異なるクロック同期およびタイミングバジェット管理が必要になります。パッケージ内外をまたぐ信号経路を考慮した、新たなタイミング設計が不可欠です。

Tj管理(レーザー温度・SerDes電力)

レーザーおよびSerDesは、いずれも温度特性に強く依存します。CPOでは、レーザーのジャンクション温度(Tj)管理とSerDes電力の最適化が、安定動作と長期信頼性の鍵となります。

冗長化設計と交換不能問題への対応

CPOでは、光部品とASICが同一パッケージ内に統合されるため、従来のプラガブル光モジュールのような容易なフィールド交換は一般的に困難になります。そのため、システムレベルでの冗長化設計、故障時の影響最小化を前提としたアーキテクチャ設計、さらには統合体としてのMTTF設計が重要となります。

OIF/IEEEによる標準化動向

CPOでは従来と異なり、仕様を定義する境界が激減し、実装の先行の後に標準化が制定され、システム主導となるため、システムごとに最適解が異なり、標準達成よりも実力が重視されるようになります。このため、OIFやIEEEによる標準化はシステム要件との整合をどのように実現するかが、重要な課題になります。

5. SYCATUSが支援するCPOレーザー開発の最前線

CPOにおいてレーザー光源は、リンク性能だけでなく、システム全体の信頼性や熱設計、PHYマージンを左右する中核コンポーネントです。特に、低RIN・狭線幅といった特性は、CPO特有の光源共用・高密度実装環境において、従来以上に重要な意味を持ちます。

CPOの設計思想においては、レーザー光源は単に規格に満足するだけではなく、CPOの性能最大化のための最適化が要求されます。このため、レーザー光源のRIN・線幅の評価には、高い測定確度と再現性が求められます。

SYCATUSでは、こうしたCPO向け要件を満たすレーザー開発および評価を支援するため、光源の雑音特性の定量評価に必要な計測ソリューションを提供しています。

ELSFP光源の特長

ELSFP光源は、CPO用途を想定して設計されたレーザー光源であり、低RIN・狭線幅特性を両立することが必要です。

さらに、高密度実装環境で問題となりやすい温度上昇を考慮し、高温動作条件下でも安定した特性を維持することが求められます。

これらの特性が、SiPhモジュレータとの組み合わせや、将来的なコヒーレントCPOへの展開も視野に入れた光源選定の要件となります。

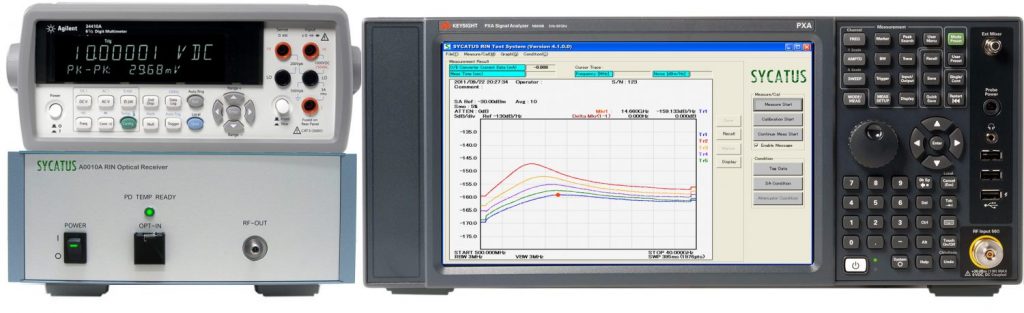

A0010AによるELSFPのRIN特性評価

CPOにおけるレーザー評価では、RIN(Relative Intensity Noise)の定量評価が不可欠です。RINは受信SNRやシステムマージンに直結するため、PHY設計段階での把握が求められます。

SYCATUSのA0010A RIN測定システムは、高感度、低ノイズの50 GHz光レシーバとKeysight社の高性能Xシリーズシグナルアナライザにより、世界最大の50 GHzの測定帯域幅を実現し、SYCATUSが開発した独自の校正方法により、高い精度と再現性を実現します。

A0010Aを用いたRIN特性評価により、ELSFP光源のノイズ特性を高精度に測定・解析することが可能です。これにより、設計段階での光源比較や、システム要件に対する適合性評価を定量的に行うことができます。

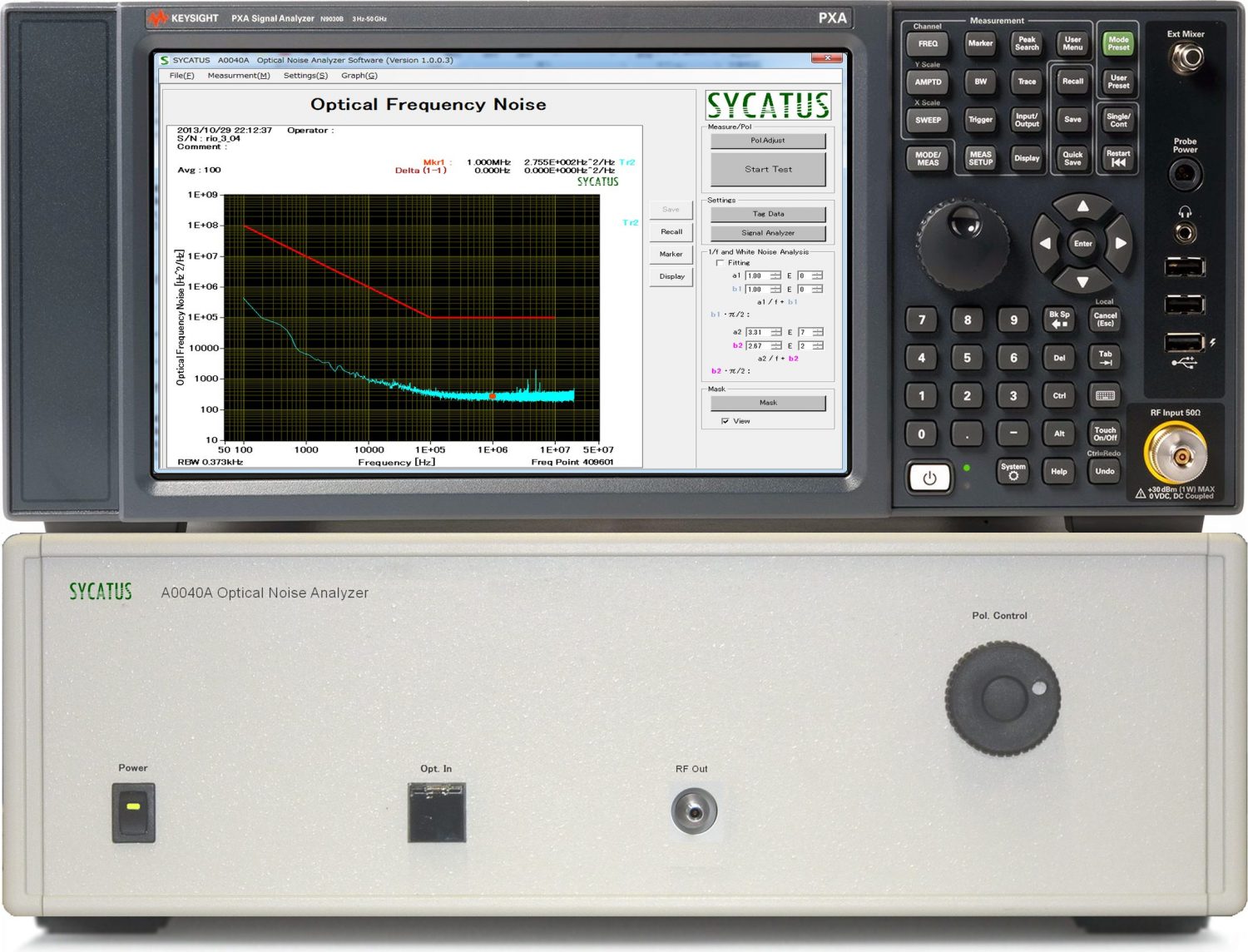

A0040AによるELSFPの線幅特性

将来的な高速化やコヒーレントCPOを見据えた場合、レーザー線幅は極めて重要な評価指標となります。線幅は位相雑音や伝送性能に影響を与え、特に高次変調方式ではシステム限界を左右します。

SYCATUSの光雑音アナライザーA0040Aは、レーザー線幅を光周波数ノイズのパワースペクトル密度として評価する業界初のソリューションです。

A0040Aを用いることで、ELSFP光源の線幅特性を高分解能で評価することができ、CPO用途における将来拡張性を含めた検討が可能となります。

SYCATUS製品の実績

SYCATUSのレーザー評価ソリューションは、研究開発用途から量産検討フェーズまで、幅広い現場での導入実績を有しています。CPO、SiPh、光エンジン統合といった最先端領域において、設計・評価・実装をつなぐ実践的なツールとして活用されています。

関連ブログ:

6. 2025年以降もNVIDIA CPOが注目される理由

NVIDIAのCPOは、特定世代のGPUに限定された技術ではなく、AIインフラのスケーラビリティと電力効率を両立させるための中長期的なアーキテクチャ戦略として位置付けられています。AIモデルの継続的な巨大化やデータセンター電力制約が続く限り、光電融合技術の重要性は高まると考えられます。

GPU、スイッチ、ネットワークを一体として設計できるNVIDIAの強みは、CPOによってさらに強化されていくと考えられます。

7. CPOレーザー評価関連製品に関するお問い合わせ

SYCATUSでは、CPO向けレーザー評価に対応した製品・ソリューションを提供しています。CPOレーザー評価関連製品についてご興味がおありの企業様は、お気軽にご相談ください。