Due to the rapid evolution of generative AI, data center design is undergoing a major shift from a focus on computational performance to one prioritizing I/O efficiency. As inter-GPU communication increases, electrical I/O efficiency and power consumption have become critical design challenges. In this context, CPO (Co-Packaged Optics), a new interconnect technology based on opto-electronic integration promoted by NVIDIA, is attracting significant attention. CPO is positioned as a key implementation architecture for enhancing the communication and power efficiency of the entire AI infrastructure, including GPUs, switches, and networks.

This article outlines the architectural transformation and physical layer requirements brought about by NVIDIA’s CPO, while also introducing SYCATUS’s measurement solutions and ELSFP light source initiatives designed to support the development and evaluation of lasers for CPO.

Table of Contents

- 1. Data Center Economics in the AI Era and the I/O Barrier

- Inter-GPU Communication Driven by Massive AI Models — The Evolution of NVIDIA NVLink

- Pressure on Data Center Operating Costs (Power and Rack Density)

- The Current Situation Where the Limits of Electrical I/O Are Hindering Improvements in GPU and Switch Performance

- The Impact on the Market of NVIDIA’s Commitment to CPO (Co-Packaged Optics)

- The Industrial Value of Securing “Leadership in AI Fabric”

- 2. The Roadmap for Next-Generation Infrastructure Envisioned by Opto-Electronic Convergence

- The Energy Efficiency (pJ/bit) Barrier That Electrical Wiring Cannot Overcome

- Why CPO Will Become the Core Technology for NVIDIA Quantum-X GPUs (Blackwell/Rubin) and Switches

- Future Prospects: Coherent CPO, SiPh (Silicon + Photonics), and Chiplet Integration

- Where Do Challenges Arise with the Conventional OSFP Approach?

- 3. Structural Transformation Brought About by CPO Architecture

- Conceptual Benefits of Integrating the Optical Engine into the Package

- The Implications of SerDes Distances Reducing to the Millimeter Range (Loss Reduction and SI Improvement)

- Changes in Design Philosophy Resulting from the Shift in the “Electrical to Optical” Conversion Point

- Signal Loss and Power Reduction Achieved by Eliminating PCB Traces and Connectors

- CPO-Specific Challenges: Alignment, Mounting, Reliability, and Maintainability

- 4. Physical Layer (PHY) Requirements for CPO

- SiPh Modulators (Silicon Photonics Modulators)

- PAM4 → Future Deployment of Coherent CPO

- Laser Noise Characteristics (RIN, Linewidth)

- Optical Fiber Array Coupling, Lens Arrays, and Submicron Alignment

- Impedance, Jitter, and CTLE/DFE Requirements for Ultra-Short-Reach SerDes (224G/112G)

- Toward an Era of Channel Loss Limits (<5 dB)

- Clock Synchronization and Timing Budget Redesign

- Tj Management (Laser Temperature and SerDes Power)

- Redundancy Design and Addressing Non-Interchangeability Issues

- Standardization Trends by OIF/IEEE

- 5. The Cutting Edge of CPO Laser Development Supported by SYCATUS

- 6. Why NVIDIA CPO Will Remain in the Spotlight in 2025 and Beyond 2026

- 7. Inquiries Regarding CPO Laser Evaluation Products

1. Data Center Economics in the AI Era and the I/O Barrier

Inter-GPU Communication Driven by Massive AI Models — The Evolution of NVIDIA NVLink

With the evolution of generative AI and large language models (LLMs), the primary battleground for performance competition in data centers is shifting from simple computational performance to inter-GPU communication (I/O).

NVIDIA has achieved GPU scaling through high-speed interconnects centered on NVLink. The Blackwell generation introduces 5th-generation NVLink and the NVLink Switch, delivering up to 1.8 TB/s of bandwidth per GPU and establishing an infrastructure capable of connecting up to 576 GPUs.

At the same time, as AI clusters continue to grow in scale, demands for system-wide communication bandwidth and power efficiency continue to rise, making the evolution of I/O architecture a critical focus.

Pressure on Data Center Operating Costs (Power and Rack Density)

As AI models grow in size, the following challenges have become apparent:

- Exponential increase in inter-GPU traffic

- Limitations on the number of ports and bandwidth of switch ASICs

- Increased transmission loss and power consumption due to electrical I/O

The Current Situation Where the Limits of Electrical I/O Are Hindering Improvements in GPU and Switch Performance

As a result of the above, data center operators are facing the triple constraints of power costs, rack density, and cooling capacity. Electrical I/O has become a bottleneck for the entire system, and simply improving the performance of individual GPUs or switches is no longer sufficient to enhance AI processing capabilities.

The Impact on the Market of NVIDIA’s Commitment to CPO (Co-Packaged Optics)

Against this backdrop, NVIDIA’s full-scale commitment to CPO (Co-Packaged Optics) is more than just the adoption of a technological trend. It should be viewed as a “strategic choice to seize control of the AI fabric.”

The company that controls I/O will define the architecture of next-generation AI infrastructure. CPO will be the core technology enabling this.

The Industrial Value of Securing “Leadership in AI Fabric”

Securing leadership in AI fabric is a critical factor in significantly enhancing industrial competitiveness by dominating the computational foundation of AI. By improving data center efficiency, reducing costs and environmental impact, and maximizing AI performance—while leading the way in setting industry standards—companies can establish a competitive advantage.

Furthermore, through integration with cutting-edge technologies such as photonics and quantum computing, this will create new markets and business models, serving as the foundation that shapes the future industrial landscape.

2. The Roadmap for Next-Generation Infrastructure Envisioned by Opto-Electronic Convergence

The Energy Efficiency (pJ/bit) Barrier That Electrical Wiring Cannot Overcome

As the length of electrical I/O wiring increases,

- Increased power consumption by SerDes to compensate for losses

- Deterioration of clock jitter and signal integrity (SI)

cannot be avoided. Furthermore, because electrical wiring has low impedance (*), power consumption increases even further.

With current state-of-the-art technology, there have been reports of achieving less than 1 pJ/bit under specific conditions. However, in real-world system environments—including data center-scale implementations, high-bandwidth SerDes, and long-distance cabling—energy efficiency in the range of several pJ/bit remains a practical design target.

On the other hand, optical interconnects offer the following advantages:

- Low-loss characteristics independent of distance

- High bandwidth and low power consumption

making sub-pJ/bit energy efficiency a realistic option.

*Impedance: A metric indicating electrical resistance (the difficulty of current flow) in an AC circuit. Relative to the voltage amplitude required for communication, lower impedance results in higher power consumption.

Why CPO Will Become the Core Technology for NVIDIA Quantum-X GPUs (Blackwell/Rubin) and Switches

NVIDIA Quantum-X is an AI fabric architecture that integrates:

- GPUs (Blackwell / Rubin)

- NVLink switches

- Data center network

into a single, optimized AI fabric architecture.

Within this structure, “where the conversion from electrical to optical signals occurs” is a critical factor that determines the overall efficiency of the system.

CPO simultaneously resolves I/O energy and scalability issues by:

- Directly integrating the optical engine into the switch/SoC package

- Reducing electrical wiring lengths to the millimeter range

Note 1: What are NVIDIA Quantum and Quantum-X?

NVIDIA Quantum is a high-speed network platform based on InfiniBand, while Quantum-X refers to a design philosophy that optimizes the entire AI data center as a single computing foundation.

NVIDIA’s Co-Packaged Optics (CPO) switches, which integrate silicon photonics, are positioned as the networking foundation for next-generation AI. NVIDIA explains that this achieves significant improvements in power efficiency and network resilience compared to traditional pluggable configurations. (Reference: NVIDIA シリコンフォトニクス│NVIDIA Corporation)

Note 2: Examples of Companies Participating in NVIDIA CPO — TSMC, etc.

NVIDIA has not disclosed details regarding which specific areas each partner company is responsible for in the design and implementation of CPO. However, based on information disclosed to date, it is known that the CPO ecosystem includes companies with strengths in optical devices, packaging, and manufacturing technologies, such as Ayar Labs, Browave, Coherent, Corning, Fabrinet, Foxconn, Lumentum, Senko, SPIL, Sumitomo Electric Industries, TFC, and TSMC.

This group of companies supports a diverse range of technical areas—including optical engines, optical fiber connections, advanced packaging, and mass production processes—and forms the industrial foundation that enables the NVIDIA CPO.

Reference: Nvidia's CPO is the First Step in a Long Journey│LightCounting

Future Prospects: Coherent CPO, SiPh (Silicon + Photonics), and Chiplet Integration

Coherent CPO, silicon photonics (SiPh), and chiplet integration are expected to serve as core technologies underpinning future data centers and AI infrastructure. Integrating these technologies enables high-speed, low-power, and highly integrated communication and computing, significantly improving data center efficiency and sustainability.

Where Do Challenges Arise with the Conventional OSFP Approach?

On the other hand, with conventional pluggable optical module approaches such as OSFP, it is common to place modules on switches or server front panels, which can result in relatively long electrical wiring distances from ASICs or GPUs to the modules. Since signal loss and power consumption increase along these wiring sections, compensation circuits such as equalizers are required to maintain transmission quality.

While OSFP modules themselves feature excellent thermal designs suited for high-density deployment and high-power operation, CPO is being considered as a new architecture to further reduce wiring lengths as AI clusters aim for greater bandwidth expansion and improved power efficiency.

3. Structural Transformation Brought About by CPO Architecture

The essence of CPO lies not only in the miniaturization of optical modules, but also in a fundamental shift in system design philosophy.

Conceptual Benefits of Integrating the Optical Engine into the Package

In CPO, optical I/O is placed in close proximity to the SoC. This reduces the distance from the SerDes to the optical conversion to the millimeter range, significantly reducing loss, reflection, and the emission and intrusion of noise.

The Implications of SerDes Distances Reducing to the Millimeter Range (Loss Reduction and SI Improvement)

By shortening SerDes trace lengths, the following become possible:

- Simplification of TX/RX compensation circuits

- Reduction in power consumption

- Expansion of SI (Signal Integrity) margins

This represents a realm that could not be achieved with conventional board-level design.

Changes in Design Philosophy Resulting from the Shift in the “Electrical to Optical” Conversion Point

As the conversion point from electrical to optical signals moves closer to the processor, I/O design shifts from a “division of labor, boundary specifications, and margin-stacking” approach to an “integration, borderless, and performance-maximization” design.

Signal Loss and Power Reduction Achieved by Eliminating PCB Traces and Connectors

By reducing PCB traces and connectors, signal loss and power consumption are minimized, enabling simpler and more efficient system designs. This achieves both improved performance and reduced operating costs.

CPO-Specific Challenges: Alignment, Mounting, Reliability, and Maintainability

On the other hand, CPO presents unique challenges, including sub-micron-level high-precision alignment, assembly yield, long-term reliability, and maintainability. In particular, addressing laser characteristics, thermal management, and the difficulty of replacing components in the event of failure is critical. Overcoming these challenges through standardization and design innovations is key to ensuring the widespread adoption of next-generation infrastructure centered on CPO and maintaining competitiveness.

4. Physical Layer (PHY) Requirements for CPO

In CPO, traditional design methods that optimize optical, electrical, thermal, and mechanical aspects separately are no longer effective. Because opto-electronic integration occurs within the package, physical layer (PHY) requirements become more stringent and highly interdependent than ever before.

The following outlines the PHY requirements that are particularly critical for CPO.

SiPh Modulators (Silicon Photonics Modulators)

Optical modulators in CPO require high-speed, low-loss designs based on silicon photonics (SiPh). Given the constraints of in-package implementation, it is necessary to simultaneously meet bandwidth, power consumption, and thermal stability requirements, making coordinated design with electrical drivers and control circuits essential.

PAM4 → Future Deployment of Coherent CPO

While PAM4 modulation is the mainstream technology in the current generation, considering further bandwidth expansion and link distance flexibility, the future deployment of coherent CPO is also on the horizon. In that case, requirements for laser linewidth and phase noise will become even more stringent, and the very prerequisites for PHY design will change.

Laser Noise Characteristics (RIN, Linewidth)

The laser’s RIN (Relative Intensity Noise) and linewidth are critical parameters that determine the overall SNR and margin of the CPO system. Particularly in shared-source and high-density deployment environments, even slight differences in laser noise characteristics can affect the performance of numerous links, making quantitative evaluation and management essential.

When evaluating lasers for CPO, it is necessary to measure optical noise characteristics—including RIN and linewidth—with high bandwidth and high resolution, and to evaluate them in accordance with actual PHY requirements. Please click here to view the list of SYCATUS laser evaluation products that enable these measurements and analyses.

Optical Fiber Array Coupling, Lens Arrays, and Submicron Alignment

CPOs inherently require high-density optical coupling using optical fiber arrays and lens arrays. Consequently, submicron-precision alignment technology is essential, and comprehensive implementation techniques—including mechanical tolerances, temperature variations, and long-term reliability—are required.

Impedance, Jitter, and CTLE/DFE Requirements for Ultra-Short-Reach SerDes (224G/112G)

On the electrical side, ultra-short-reach SerDes of the 112G and 224G classes are used. With wiring lengths in the millimeter range, channel characteristics change significantly, requiring optimal solutions for impedance mismatch, jitter, and CTLE/DFE design concepts that differ from conventional approaches.

Toward an Era of Channel Loss Limits (<5 dB)

In CPO, the ASIC and optical engine are housed within the same package, significantly reducing the electrical channel length. As a result, channel loss can be substantially reduced compared to conventional board-level transmission.

In such a low-loss environment, the approach to optimizing SerDes and PHY margin designs may change. However, compensation circuits such as equalizers still play a critical role in high-speed signal transmission, and appropriate design and optimization are required even in a CPO environment.

Clock Synchronization and Timing Budget Redesign

CPO requires clock synchronization and timing budget management that differ from conventional board-level designs. A new timing design that accounts for signal paths spanning both inside and outside the package is essential.

Tj Management (Laser Temperature and SerDes Power)

Both lasers and SerDes are highly dependent on temperature characteristics. In CPO, managing the laser junction temperature (Tj) and optimizing SerDes power are key to stable operation and long-term reliability.

Redundancy Design and Addressing Non-Interchangeability Issues

In CPO, because optical components and ASICs are integrated within the same package, easy field replacement—as seen in conventional pluggable optical modules—is generally difficult. Therefore, system-level redundancy design, architectural design aimed at minimizing the impact of failures, and MTTF design for the integrated unit as a whole are critical.

Standardization Trends by OIF/IEEE

Unlike traditional approaches, CPO significantly reduces the scope of defined specifications. Since standardization follows implementation and is system-driven, the optimal solution varies by system, and practical performance takes precedence over strict compliance with standards. Consequently, a key challenge for standardization by OIF and IEEE is how to achieve alignment with system requirements.

5. The Cutting Edge of CPO Laser Development Supported by SYCATUS

In CPO systems, the laser source is a core component that determines not only link performance but also the reliability of the entire system, thermal design, and PHY margin. In particular, characteristics such as low RIN and narrow linewidth are more critical than ever in the CPO-specific environment of shared light sources and high-density packaging.

In CPO design philosophy, laser sources must not only meet specifications but also be optimized to maximize CPO performance. Consequently, evaluating the RIN and linewidth of laser sources requires high measurement accuracy and reproducibility.

To support the development and evaluation of lasers that meet these CPO requirements, SYCATUS provides measurement solutions necessary for the quantitative evaluation of light source noise characteristics.

Features of ELSFP Light Sources

The ELSFP light source is a laser light source designed specifically for CPO applications, requiring the simultaneous achievement of low RIN and narrow linewidth characteristics.

Furthermore, considering the temperature rise that often becomes an issue in high-density mounting environments, these sources must maintain stable performance even under high-temperature operating conditions.

These characteristics form the requirements for selecting light sources, taking into account their combination with SiPh modulators and their potential future deployment in coherent CPOs.

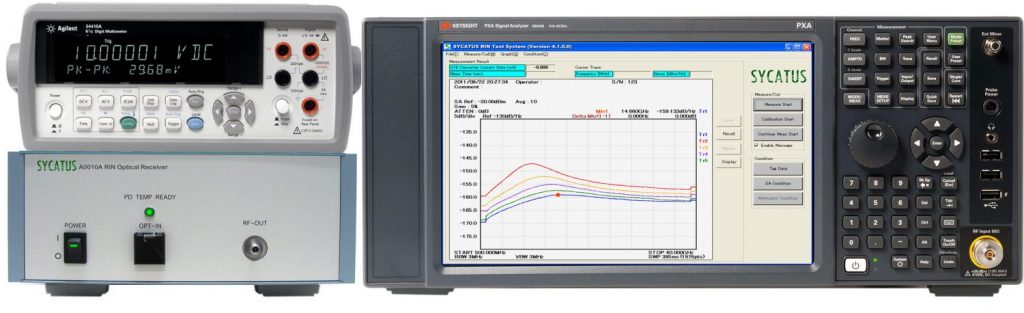

RIN Characterization of ELSFP Using the A0010A

In laser evaluation for CPOs, quantitative assessment of RIN (Relative Intensity Noise) is essential. Since RIN directly affects receiver SNR and system margin, it must be determined during the PHY design phase.

SYCATUS’s A0010A RIN measurement system achieves 50 GHz measurement bandwidth using a high-sensitivity, low-noise 50 GHz optical receiver and Keysight’s high-performance X-Series signal analyzer. It also delivers high accuracy and reproducibility through a proprietary calibration method developed by SYCATUS.

RIN characterization using the A0010A enables high-precision measurement and analysis of the noise characteristics of ELSFP light sources. This allows for quantitative comparison of light sources and evaluation of compliance with system requirements during the design phase.

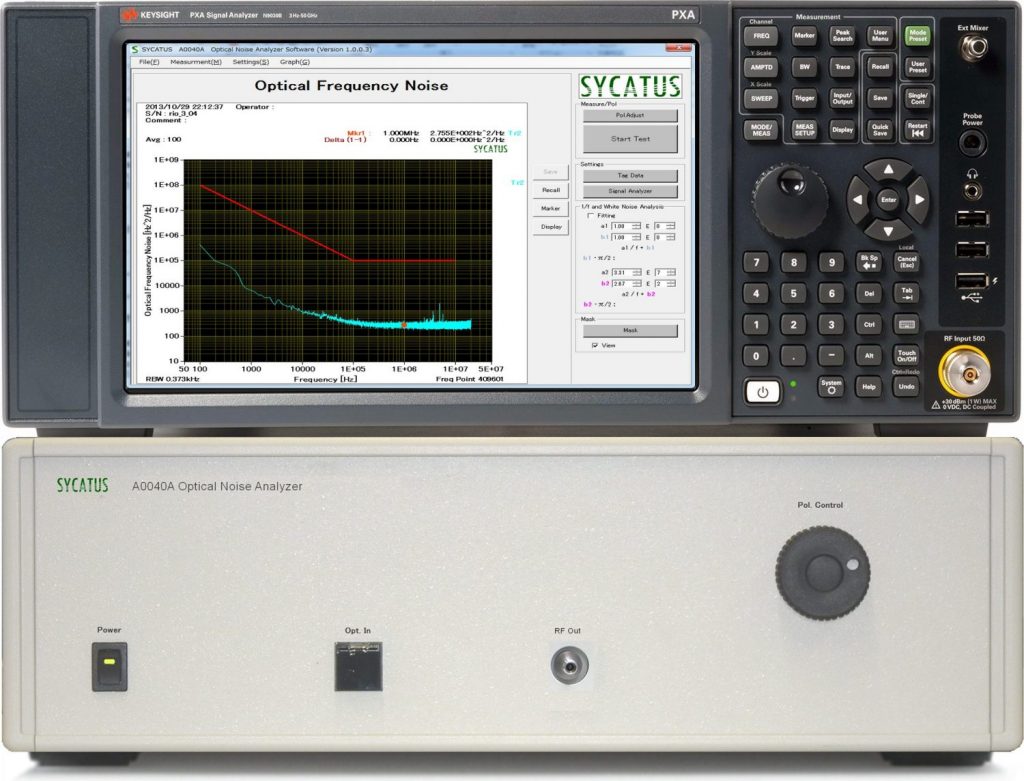

Linewidth Characterization of ELSFP Using the A0040A

With an eye toward future high-speed applications and coherent CPO, laser linewidth is a critically important evaluation metric. Linewidth affects phase noise and transmission performance, and particularly in higher-order modulation schemes, it determines system limits.

SYCATUS’s optical noise analyzer A0040A is the industry’s first solution to evaluate laser linewidth as the power spectral density of optical frequency noise across a broad bandwidth of 255 MHz.

Using the A0040A enables high-resolution evaluation of the linewidth characteristics of ELSFP light sources, facilitating assessments that include future scalability for CPO applications.

Track Record of SYCATUS Products

SYCATUS’s laser evaluation solutions have a proven track record of deployment across a wide range of environments, from research and development to mass production planning phases in many countries around the world. They are utilized as practical tools that bridge design, evaluation, and implementation in cutting-edge fields such as CPO, SiPh, and integrated optical engines.

Related Blog Posts:

- Do you know what Relative Intensity Noise is and how to measure it?

- “Light Spectrum” and “Linewidth”: What is the difference between the two noise indicators in optical measurement?

6. Why NVIDIA CPO Will Remain in the Spotlight in 2025 and Beyond 2026

NVIDIA’s CPO is not a technology limited to a specific generation of GPUs; rather, it is positioned as a mid- to long-term architectural strategy designed to balance scalability and power efficiency in AI infrastructure. As long as AI models continue to grow in size and data center power constraints persist, the importance of opto-electronic integration technology is expected to increase.

NVIDIA’s strength in designing GPUs, switches, and networks as an integrated whole is expected to be further enhanced by CPO.

7. Inquiries Regarding CPO Laser Evaluation Products

SYCATUS offers products and solutions compatible with CPO laser evaluation. Companies interested in CPO laser evaluation products are welcome to contact us.